探針臺

Probe Stations

文章內容參考論文:“O-band low loss and polarization insensitivity bilayer and double-tip edge coupler”

文章使用設備:光纖波導耦合系統(tǒng)

硅基光子集成電路(PIC)作為光通信、計算和傳感等領域的核心技術,正推動著高速光互連與集成光子學的飛速發(fā)展。然而,硅光子芯片與光纖的高效耦合始終是制約其大規(guī)模應用的關鍵挑戰(zhàn)之一。傳統(tǒng)端面耦合器在O波段(1260-1360 nm)因硅波導的強雙折射特性,面臨顯著的偏振相關損耗(PDL),導致TE和TM模式的耦合效率差異較大。如何在保持制造工藝兼容性的同時實現(xiàn)低損耗、寬帶寬且偏振不敏感的耦合,成為學術界與工業(yè)界共同關注的難題。

近日,有教授團隊提出了一種雙層雙尖端端面耦合器,通過創(chuàng)新結構與工藝設計,成功在O波段實現(xiàn)TE/TM雙模高效耦合。實驗結果表明,TE模式耦合損耗低至1.18 dB/facet,TM模式耦合損耗僅為1.46 dB/facet(1310 nm波長),且在整個O波段內性能穩(wěn)定,兼容商用硅光工藝。該成果為解決O波段端面耦合器的偏振敏感問題提供了有效方案。研究以“O-Band Low Loss and Polarization Insensitivity Bilayer and Double-tip Edge Coupler”為題。

端面耦合器是實現(xiàn)芯片與光纖連接的核心器件,其性能直接取決于波導模場與光纖模場的匹配程度。本文提出的雙層雙尖端端面耦合器(圖1)通過協(xié)同優(yōu)化波導結構與雙尖端設計,顯著降低了模式場失配與偏振依賴性。本文提出了一種基于雙層與雙尖端邊緣耦合器的創(chuàng)新方案,旨在實現(xiàn)O波段光纖與芯片間的高效耦合,同時最大限度降低偏振態(tài)損耗(PDL)。通過采用多重刻蝕工藝,我們有效降低了波導的縱向模式約束,實現(xiàn)了橫向電場模(TE)和橫向磁場模(TM)的高耦合效率。實驗驗證表明,該邊緣耦合器在整個O波段范圍內性能優(yōu)異,當與具有模式場直徑(MFD)4μm的透鏡光纖耦合時,兩種偏振方向的耦合損耗均低于2 dB/端面。

圖1:雙層雙尖端端面耦合器示意圖

圖 1:

(a)雙層和雙頭邊緣耦合器的示意圖。

(b)邊緣耦合器的橫截面圖像。

(c)高度過渡過程的橫截面圖像。

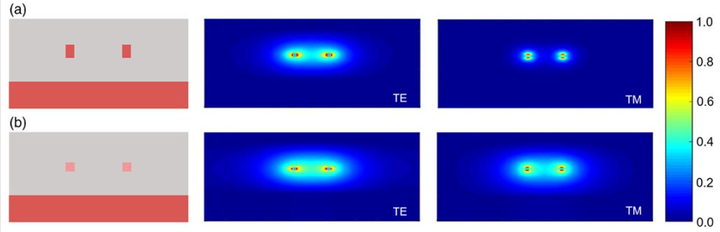

通過仿真分析發(fā)現(xiàn),傳統(tǒng)220 nm高度的波導對TM模式的強限制導致其有效模場面積遠小于TE模式(圖2a)。為此,團隊采用另一種常用的150 nm波導高度(圖2b),通過降低縱向模式束縛,使TM模場面積大幅提升。其中E?和E?分別表示光纖模式與芯片波導模式的復電場振幅。為提升耦合效率,需設計與輸入光纖模式高度匹配的波導結構。如圖2(a)和2(b)所示,我們通過仿真分析計算了兩種不同高度波導結構在1310納米波長下的TE和TM模式場分布。從圖2(a)可見,TE模式的有效模面積明顯大于TM模式。這源于1310納米波長下波導的強雙折射特性——220納米高的波導對TM模式具有更強的約束作用,導致其模尺寸更小。因此我們將波導高度調整為150納米以降低TM模式的約束效應。如圖2(b]仿真結果所示,在此配置下TE和TM模式的有效模面積基本保持一致。

綜上,通過仿真分析發(fā)現(xiàn),傳統(tǒng)220 nm高度的波導對TM模式的強限制導致其有效模場面積遠小于TE模式(圖2a)。為此,團隊采用另一種常用的150 nm波導高度(圖2b),通過降低縱向模式束縛,使TM模場面積大幅提升。

圖2:雙頭波導以及TE和TM模式場分布的橫截面圖像

圖2:雙頭波導以及TE和TM模式場分布的橫截面圖像。

(a) 220 nm 高。

(b) 150 nm 高。

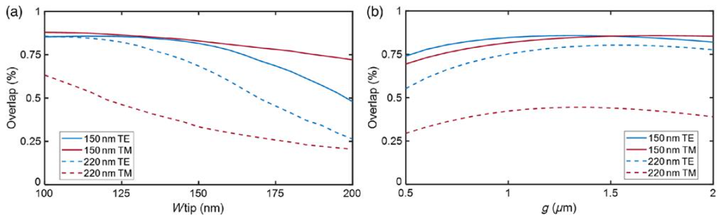

為定量分析兩種波導結構的差異并實現(xiàn)更高耦合效率,我們針對尖端波導寬度和間距進行了優(yōu)化設計,并計算了其與4μm MFD透鏡光纖模式的重疊度。首先,我們對尖端波導寬度進行了優(yōu)化模擬(如圖3(a)所示)。圖中實線和虛線分別代表高度為150納米和220納米的波導結構,紅色和藍色線條分別對應TE和TM模式。從仿真結果可見,紅色實線的整體重疊度比紅色虛線高出20%以上,充分證明了我們設計方法的有效性。當波導結構高度為220納米時,TE和TM模式的重疊度存在顯著差距,難以同時實現(xiàn)高效耦合與光子帶隙(PDL)的雙重目標。然而,當波導結構高度為150納米時,在100至150納米的尖端寬度范圍內,兩種模式的重疊度均接近80%以上。

圖3:220 nm和150 nm 高度下不同偏振耦合效率分析

圖3:計算的模式重疊度隨(a)Wtip和(b)g的變化關系

團隊設計的器件是在SOI晶圓上制造的,其頂部硅層厚度為220納米,埋入式二氧化硅層厚度為2μm。該器件設計分為兩層結構,通過多道蝕刻工藝完成。首先使用電子束光刻(EBL)技術,在晶圓表面旋涂ZEP520電子束抗蝕劑。隨后利用EBL將圖案轉印至抗蝕劑層。接著通過電子束蒸發(fā)沉積10/50納米厚的鉻/金金屬層,并進行剝離處理去除多余金屬,最終形成圖案化結構。在第二步EBL工藝中,將第一層結構轉印至電子束抗蝕劑層。為將結構轉印至硅層,采用電感耦合等離子體(ICP)蝕刻工藝對頂部硅層進行220納米深度蝕刻。在另一輪EBL和ICP工藝中,將第二層結構轉印至硅層并蝕刻70納米。最后通過等離子體增強化學氣相沉積法在頂部沉積2μm厚的二氧化硅包覆層。圖6(a)展示了器件的光學顯微鏡圖像,插圖為邊緣耦合器的放大視圖。圖6(b)-6(d)為圖6(a]插圖中標記區(qū)域的掃描電子顯微鏡(SEM)圖像。

團隊采用電子束曝光(EBL)與感應耦合等離子體(ICP)刻蝕等技術,通過兩次EBL步驟分別定義雙層結構。第一層刻蝕深度為220 nm,第二層刻蝕70 nm,最終形成150 nm高度的雙尖端波導(圖4b-d)。通過精確控制刻蝕參數(shù),團隊實現(xiàn)了納米級精度的波導形貌,并利用等離子體增強化學氣相沉積(PECVD)技術沉積2 μm厚的SiO?包層,確保器件長期穩(wěn)定性。

圖4:端面耦合器顯微圖

圖4:

(a)單芯片切割后的光學顯微鏡圖像。

(b)-(d)制備的邊緣耦合器的掃描電鏡圖像。

為表征所制備的邊緣耦合器性能,我們采用波長范圍在1260至1360納米之間的可調諧激光器作為輸入光源。通過光功率計測量芯片輸出端的耦合功率,并使用偏振控制器將輸入光的偏振態(tài)控制在TE和TM模式之間。耦合裝置 該裝置由兩個精密六軸對準臺、2個觀察系統(tǒng)(垂直+水平)和一個芯片支架組成,如圖7插圖所示。我們在光纖支架兩側各固定一根4-MM MFD透鏡光纖,并通過調整六軸對準臺使功率計測得的光功率最大化。通過調節(jié)輸入光波長和偏振控制器,我們對器件在整個0波段范圍內的TE和TM耦合損耗進行了表征。圖8展示了器件的測試與仿真性能對比,其中實線和虛線分別代表實驗與仿真結果,紅色和藍色曲線分別對應TE和TM模式數(shù)據(jù)。觀察發(fā)現(xiàn)實驗結果雖略遜于仿真結果,但兩者呈現(xiàn)一致趨勢,充分展現(xiàn)了器件在偏振相關損耗方面的卓越性能。在1310 nm波長下,TE和TM模式耦合損耗分別測量為1.18 dB/端面和1.46 dB/端面。光譜中出現(xiàn)的噪聲源于測試過程中耦合裝置的振蕩以及光纖與芯片間的反射。在整個0波段范圍內,TE和TM模式耦合損耗分別<1.52 dB/端面和2 dB/端面。

圖5:波導耦合系統(tǒng)

該端面耦合器在O波段的高效表現(xiàn),使其成為高速數(shù)據(jù)通信(如5G和下一代數(shù)據(jù)中心)中光纖-芯片接口的理想解決方案。其低偏振敏感特性尤其適用于偏振復用系統(tǒng),可顯著降低系統(tǒng)復雜度與成本。隨著O波段在短距通信和傳感領域的廣泛應用,此類高性能耦合器有望成為下一代光子集成芯片的核心組件,推動光電子產(chǎn)業(yè)持續(xù)革新。